- 您现在的位置:买卖IC网 > Sheet目录3884 > PIC17C766T-33E/PT (Microchip Technology)IC MCU CMOS 33MHZ 16K EPRM80TQFP

Section 3 Floating-Point Unit (FPU)

Page 72 of 1336

R01UH0025EJ0300 Rev. 3.00

Sep 24, 2010

SH7261 Group

3.3.2

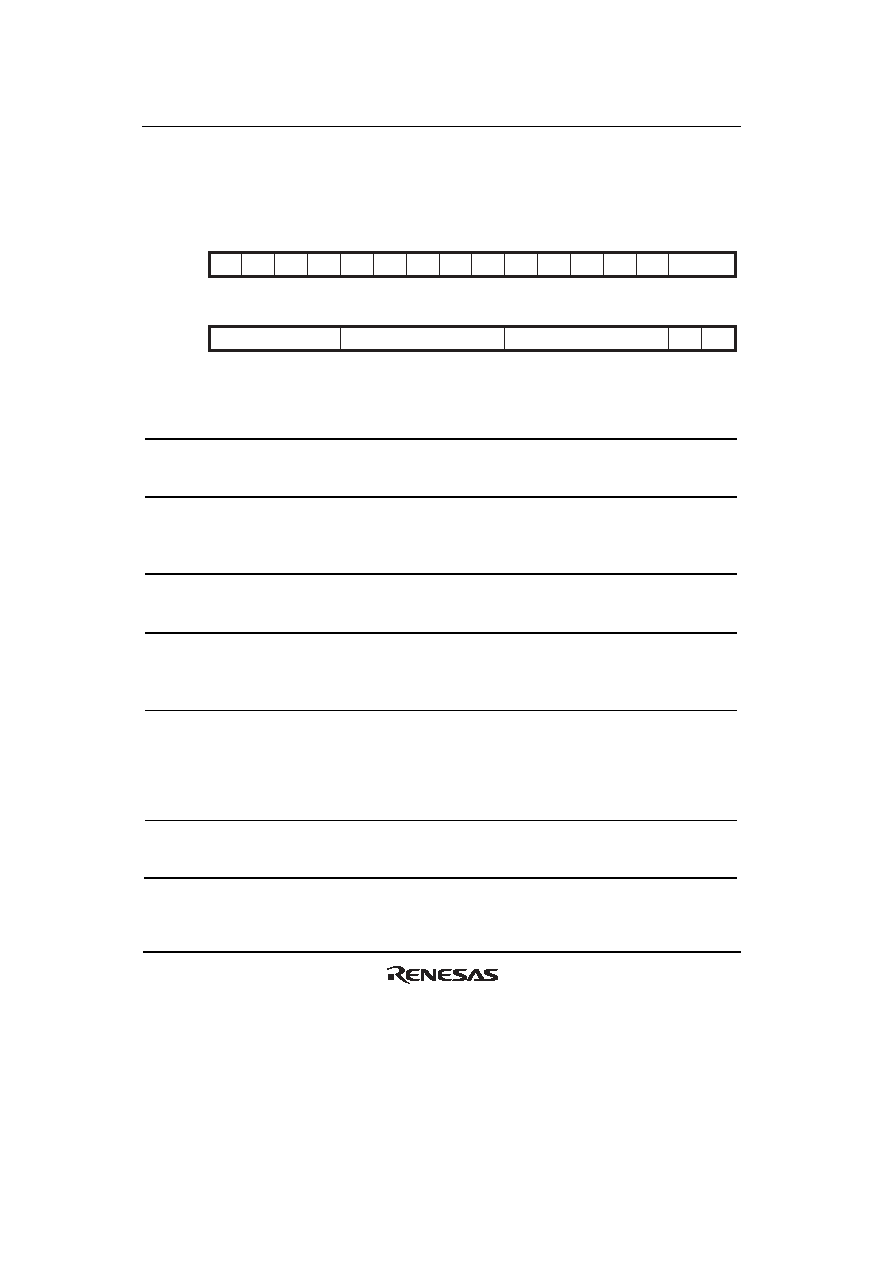

Floating-Point Status/Control Register (FPSCR)

FPSCR is a 32-bit register that controls floating-point instructions, sets FPU exceptions, and

selects the rounding mode.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

Bit:

000000000

0

00100

0000000001

Initial value:

RRRRRRRRR

R

R/W

R

R/W

Enable

Flag

Cause

RM1

QIS

SZ

PR

DN

RM0

Cause

R/W

R/W:

Bit:

Initial value:

R/W:

15

14

13

12

11

10

9876543210

00

R/W

Bit

Bit Name

Initial

Value

R/W

Description

31 to 23

—

All 0

R

Reserved

These bits are always read as 0. The write value should

always be 0.

22

QIS

0

R/W

Nonnunerical Processing Mode

0: Processes qNaN or

±∞ as such

1: Treats qNaN or

±∞ as the same as sNaN (valid only

when the V bit in FPSCR enable is set to 1)

21

—

0

R

Reserved

This bit is always read as 0. The write value should

always be 0.

20

SZ

0

R/W

Transfer Size Mode

0: Data size of FMOV instruction is 32-bits

1: Data size of FMOV instruction is a 32-bit register

pair (64 bits)

19

PR

0

R/W

Precision Mode

0: Floating-point instructions are executed as

single-precision operations

1: Floating-point instructions are executed as

double-precision operations (graphics support

instructions are undefined)

18

DN

1

R

Denormalization Mode (Always fixed to 1 in SH2A-

FPU)

1: Denormalized number is treated as zero

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC17C766T-33E/L

IC MCU CMOS 33MHZ 16K EPRM84PLCC

PIC17C766T-16E/PT

IC MCU CMOS 16MHZ 16K EPRM80TQFP

PIC17C766T-16E/L

IC MCU CMOS 16MHZ 16K EPRM84PLCC

PIC17C766-33E/PT

IC MCU CMOS 33MHZ 16K EPRM80TQFP

PIC17C766-33E/L

IC MCU CMOS 33MHZ 16K EPRM84PLCC

PIC16C54C-20/P

IC MCU OTP 512X12 18DIP

PIC17C766-16E/PT

IC MCU CMOS 16MHZ 16K EPRM80TQFP

PIC17C766-16E/L

IC MCU CMOS 16MHZ 16K EPRM84PLCC

相关代理商/技术参数

PIC17C766T-33I/L

功能描述:8位微控制器 -MCU 33MHz 16K EPRM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC17C766T-33I/PT

功能描述:8位微控制器 -MCU 32KB 902 RAM 66 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC17LC42A-08/L

功能描述:8位微控制器 -MCU 4KB 232 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC17LC42A-08/P

功能描述:8位微控制器 -MCU 4KB 232 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC17LC42A-08/PQ

功能描述:8位微控制器 -MCU 4KB 232 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC17LC42A-08/PT

功能描述:8位微控制器 -MCU 4KB 232 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC17LC42A-08I/L

功能描述:8位微控制器 -MCU 4KB 232 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC17LC42A-08I/P

功能描述:8位微控制器 -MCU 4KB 232 RAM 33 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT